Product Summary

The XC3S500E-4PQ208C Field-Programmable Gate Array is specifically designed to meet the needs of high volume, cost-sensitive consumer electronic applications. It offers densities ranging from 50,000 to five million system gates. The XC3S500E-4PQ208C builds on the success of the earlier Spartan-IIE family by increasing the amount of logic resources, the capacity of internal RAM, the total number of I/Os, and the overall level of performance as well as by improving clock management functions. Numerous enhancements derive from state-of-the-art Virtex-II technology. These XC3S500E-4PQ208C enhancements, combined with advanced process technology, deliver more functionality and bandwidth per dollar than was previously possible, setting new standards in the programmable logic industry.

Parametrics

XC3S500E-4PQ208C absolute maximum ratings: (1)Internal supply voltage: –0.5 to 1.32 V; (2)Auxiliary supply voltage: –0.5 to 3.00 V; (3)Output driver supply voltage: –0.5 to 3.75 V; (4)Input reference voltage: –0.5 to VCCO+0.5 V; (5)Voltage applied to all User I/O pins and Dual-Purpose pins: –0.5 to VCCAUX+0.5 V at Driver in a high-impedance state, –0.5 to VCCO+0.5 V at Voltage applied to all Dedicated pins; (6)Junction temperature: 125 ℃ at VCCO < 3.0V, 105 ℃ at VCCO > 3.0V; (7)Storage temperature: –65 to 150 ℃.

Features

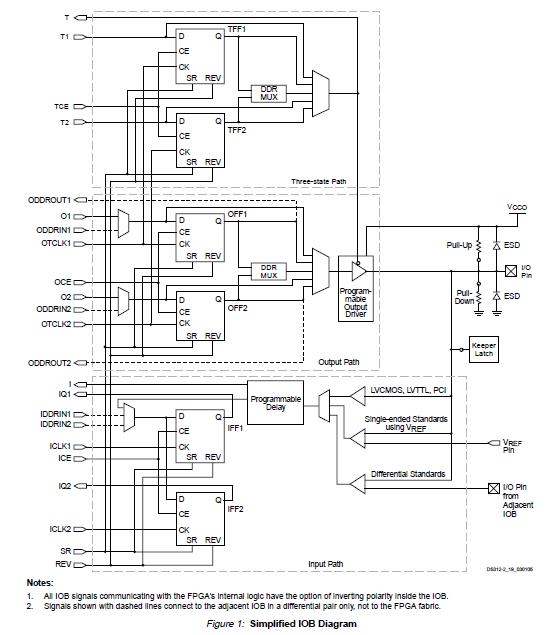

XC3S500E-4PQ208C features: (1)Very low cost, high-performance logic solution for high-volume, consumer-oriented applications; (2)Proven advanced 90-nanometer process technology; (3)Multi-voltage, multi-standard SelectIO interface pins: Up to 376 I/O pins or 156 differential signal pairs, LVCMOS, LVTTL, HSTL, and SSTL single-ended signal standards, True LVDS, RSDS, mini-LVDS differential I/O, 3.3V, 2.5V, 1.8V, 1.5V, and 1.2V signaling, Enhanced Double Data Rate (DDR) support; (4)Abundant, flexible logic resources: Densities up to 33,192 logic cells, including optional shift register or distributed RAM support, Efficient wide multiplexers, wide logic, Fast look-ahead carry logic, Enhanced 18 x 18 multipliers with optional pipeline, IEEE 1149.1/1532 JTAG programming/debug port.

Diagrams

|

XC3S1000 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||

|

XC3S1000-4FG456I |

|

IC FPGA SPARTAN 3 456FBGA |

Data Sheet |

|

|

||||||||||

|

XC3S1000-4FG676I |

|

IC FPGA SPARTAN 3 676FBGA |

Data Sheet |

|

|

||||||||||

|

XC3S1000-4FGG320C |

|

SPARTAN-3A FPGA 1M STD 320-FBGA |

Data Sheet |

|

|

||||||||||

|

XC3S1000-4FGG320I |

|

IC SPARTAN-3A FPGA 1M 320-FBGA |

Data Sheet |

|

|

||||||||||

|

XC3S1000-4FGG456C |

|

IC SPARTAN-3 FPGA 1M 456-FBGA |

Data Sheet |

|

|

||||||||||

(China (Mainland))

(China (Mainland))