Product Summary

The EPM5128JC Erasable programmable logic device represent a revolutionary step in programmable logic: they combine innovative architecture and state-of-the-art process to offer optimum performance, logic density, flexibility, and the highest speeds and densities available in general-purpose reprogrammable logic. These EPLDs of the EPM5128JC are high-speed high-density replacements for SSI and MSI TTL and CMOS packages and conventional PLDs.

Parametrics

EPM5128JC maximum ratings: (1)Vcc: -2.0 to 7.0V; (2)VPP: -2.0 to 13.5V; (3)DC input voltage: -2.0 to 7.0V; (4)DC VCC or GND current: 200 mA; (5)IOUT, DC output current per pin: -25 to 25mA; (6)Power dissipation: 1000mW; (7)Storage temperature: -65 to 150℃; (8)Ambient temperature: -65 to 135℃; (9)Junction temperature: 150℃.

Features

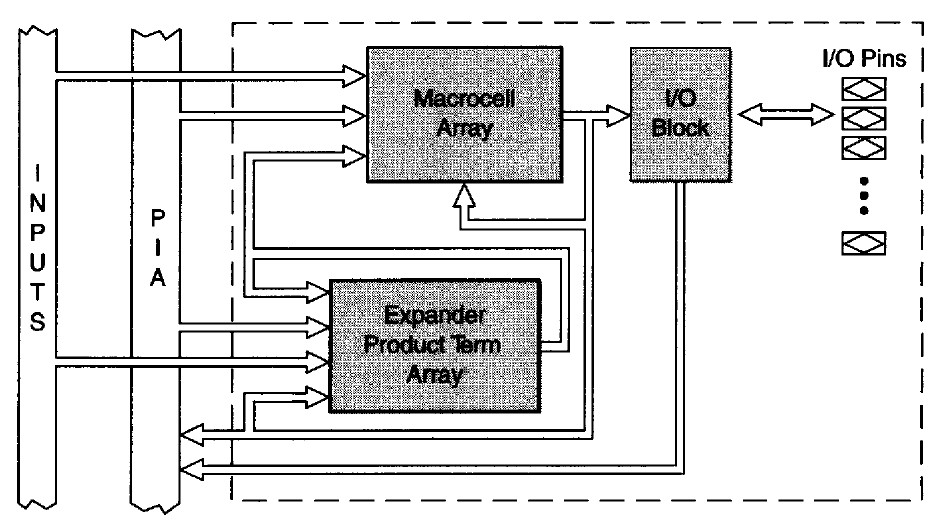

EPM5128JC features: (1)Compelete family of CMOS EPLDs solves design tasks ranging from fast 20-pin address decoders to 100-pin LSI custom peripherals; (2)The advanced MAX5000 architecture combines the speed, ease of use, and familiarity of PAL devices with the density of programmable gate arrays; (3)MAX 5000 EPLDs provide 15-ns combinatorial delays, counter frequencies up to 100MHz, pipelined data rates of 100 MHz, and high-complexity designs with true system clock rates up to 66MHz; (4)Available in a wide variety of packages, including DIP, SOIC, J-lead, PGA, and QFP formats in windowed ceramic and plastic one-time-programmable versions.

Diagrams

|

EPM5032 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EPM5032 EPLD |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EPM5128GC/GM |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EPM5128GC2 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EPM5128GM |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

EPM5128GM/883 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))