Product Summary

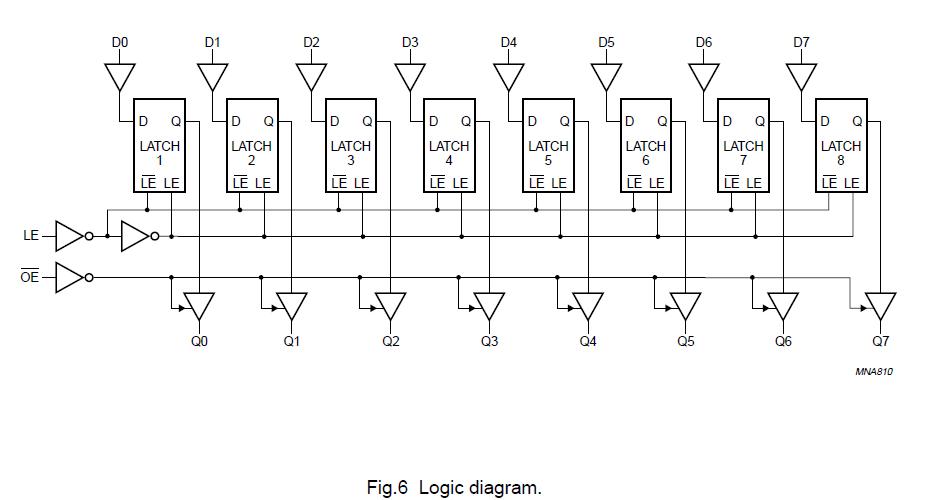

The 74LVC573APW is a high-performance, low-power, low-voltage, Si-gate CMOS device, superior to most advanced CMOS compatible TTL families. Inputs can be driven from either 3.3 or 5 V devices. In 3-state operation, outputs can handle 5 V. This feature allows the use of the 74LVC573APW as translator in a mixed 3.3 or 5 V environment. The 74LVC573APW consists of eight D-type transparent latches with 3-state true outputs. When LE of the 74LVC573APW is HIGH, data at the Dn inputs enters the latches. In this condition, the latches are transparent. When LE of the 74LVC573APW is LOW, the latches store the information that was present at the D-inputs one set-up time preceding the HIGH-to-LOW transition of LE. When OE is LOW, the contents of the eight latches are available at the outputs. When OE is HIGH, the outputs go to the high impedance OFF-state. Operation of the OE input does not affect the state of the latches.

Parametrics

74LVC573APW absolute maximum ratings: (1)VCC, supply voltage: -0.5 to +6.5 V; (2)IIK, input diode current: -50 mA max when VI < 0; (3)VI, input voltage: -0.5 to +6.5 V; (4)IOK, output diode current: ±50 mA when VO > VCC or VO < 0; (5)VO, output voltage: -0.5 to VCC + 0.5 V when output HIGH- or LOW-state; -0.5 to +6.5 V when output 3-state; (6)IO, output source or sink current: ±50 mA max when VO = 0 to VCC; (7)ICC, IGND, VCC or GND current: ±100 mA max; (8)Tstg, storage temperature: -65 to +150℃; (9)Ptot, power dissipation: 500 mW when Tamb = -40 to +125℃.

Features

74LVC573APW features: (1)5 V tolerant inputs/outputs, for interfacing with 5 V logic; (2)Supply voltage range from 1.2 to 3.6 V; (3)Inputs accept voltages up to 5.5 V; (4)CMOS low power consumption; (5)Direct interface with TTL levels; (6)High impedance when VCC = 0 V; (7)Flow-through pin-out architecture; (8)Complies with JEDEC standard no. 8-1A; (9)ESD protection: HBM EIA/JESD22-A114-A exceeds 2000 V; MM EIA/JESD22-A115-A exceeds 200 V; (10)Specified from -40 to +85℃ and -40 to +125℃.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

74LVC573APW |

NXP Semiconductors |

Latches 3.3V OCTAL D TRANS LATCH 3-S |

Data Sheet |

Negotiable |

|

||||||||||||

|

74LVC573APW,112 |

NXP Semiconductors |

Latches 3.3V OCTAL D TRANS |

Data Sheet |

|

|

||||||||||||

|

74LVC573APW,118 |

NXP Semiconductors |

Latches OCTAL TRANSPAR LATCH |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))